#### Overview

Pragmatic Semiconductor is pioneering flexible semiconductor technology, sustainably delivering edge and item-level intelligence at scale.

The Pragmatic FlexIC Foundry operates a unique and innovative process offering sustainable production and rapid innovation cycle times, coupled with a pathway to supply chain resilience.

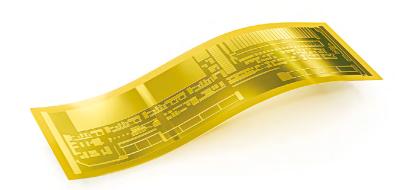

Driven by optimised, purpose-led design, our ultrathin FlexICs – flexible integrated circuits – empower innovators with connect, sense and compute capabilities to bridge our digital and physical worlds.

## Introducing Pragmatic FlexIC Platform Gen 3

Pragmatic FlexIC Platform Gen 3 providers designers with the tools to efficiently design and rapidly manufacture mixed-signal FlexICs on Pragmatic's third-generation metal-oxide thin-film transistor (TFT) technology.

- Thin, flexible form factor for novel, space-constrained applications

- Process design kit (PDK) compatible with industry standard electronic design automation (EDA) tools

- · Standard cell library accelerating design success

- · Rapid fabrication on 300 mm wafers, reducing time to market

- · Sustainable, low-carbon manufacturing

The technology excels in applications such as radio-frequency identification (RFID), multiplexing, driver and sensor readout circuitry, and basic computation.

## Technology overview

Built on a flexible substrate, the technology offers a 600 nm minimum channel dimension n-type FET, a dedicated 200 k $\Omega$ /sq resistor layer and 4.5 fF/ $\mu$ m² metal-insulator-metal capacitors. Four metal layers provide efficient routing and interconnects, with a 4  $\mu$ m routing pitch.

The technology is packaged with passivation for protection and isolation, and a redistribution layer (RDL) with aluminium metallisation for compatible attachment methods.

# Technology specifications

| Transistors   | Metal oxide thin film transistor                   | n-type FET                            |

|---------------|----------------------------------------------------|---------------------------------------|

|               | Minimum channel dimension                          | L= 0.6 μm, W= 1 μm                    |

|               | Maximum channel dimension                          | L= 1.2 μm, W= 20 μm                   |

|               | Field effect mobility                              | ~20 cm <sup>2</sup> /Vs               |

|               | $I_{DOFF}$ (L=600nm, $V_{g} = 0V$ , $V_{D} = 3V$ ) | ~ 10 fA/µm²                           |

|               | $I_{DSAT}$ (L=600nm, $V_{G}$ = 3V, $V_{D}$ = 3V)   | ~ 25µA                                |

| Resistors     | Dedicated resistor layer                           | 200 kΩ/sq.                            |

|               | Minimum line width/space                           | 0.6 μm/1.0 μm                         |

|               | Temperature performance                            | Linear -0.8 % per °C                  |

| MIMCaps       | Unit capacitance                                   | 4.5 fF/μm²                            |

|               | Leakage at 1.8 V                                   | 1x10 <sup>-16</sup> A/μm <sup>2</sup> |

| Interconnects | Independent metal routing                          | Four layers (two dedicated)           |

|               | Routing pitch                                      | 4 μm                                  |

| Packaging     | Top passivation thickness                          | 5.5 µm                                |

|               | Aluminium RDL                                      | 1.5 µm                                |

| Physical      | Total thickness                                    | ∼37 µm                                |

|               | Minimum bend radius                                | 5 mm                                  |

|               | Wafer size                                         | 300 mm                                |

|               |                                                    |                                       |

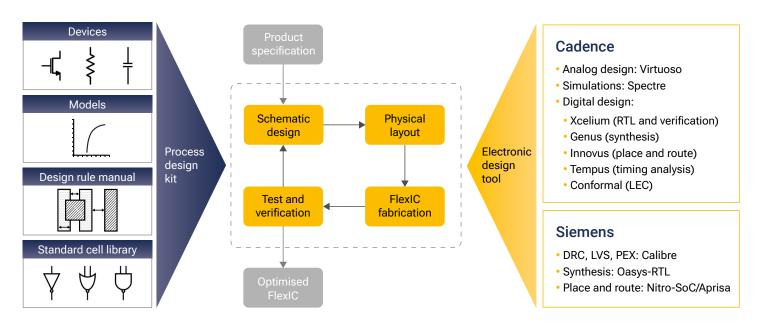

### Process design kit

Platform Gen 3's PDK gives designers the tools to accurately design circuitry for bespoke mixed-signal applications. It is compatible with industry-standard EDA tools and design flows from Cadence and Siemens and contains:

- · Primitive device library with simulation models

- Parameterized cells (PCells)

- Verification checks (DRC, LVS)

- Technology data and files

- · Design, layout, tape out manuals & guides

A standard cell library is available, providing the building blocks to accelerate design and time to market.

Pragmatic's FlexIC Foundry provides 300 mm wafer fabrication and back-end services that enable rapid innovation cycles, taking designs to production with weeks. Dedicated engineering support is on hand to support you from initial prototyping and design to high-volume manufacturing.

## **Delivery formats**

Platform Gen 3 is available on 300 mm wafers and delivered in the following formats:

Wafer on glass carrier

Wafer diced on frame

Singulated FlexICs in Gel-Box (prototyping only)

To find out more about Pragmatic's unique flexible semiconductor technology, visit: www.pragmaticsemi.com